高密度QRフライバック・コンバータ技術で電源実装の進歩を実現

国際法や新しい規格によって、電源の設計者は電源の全体的な効率向上を迫られています。

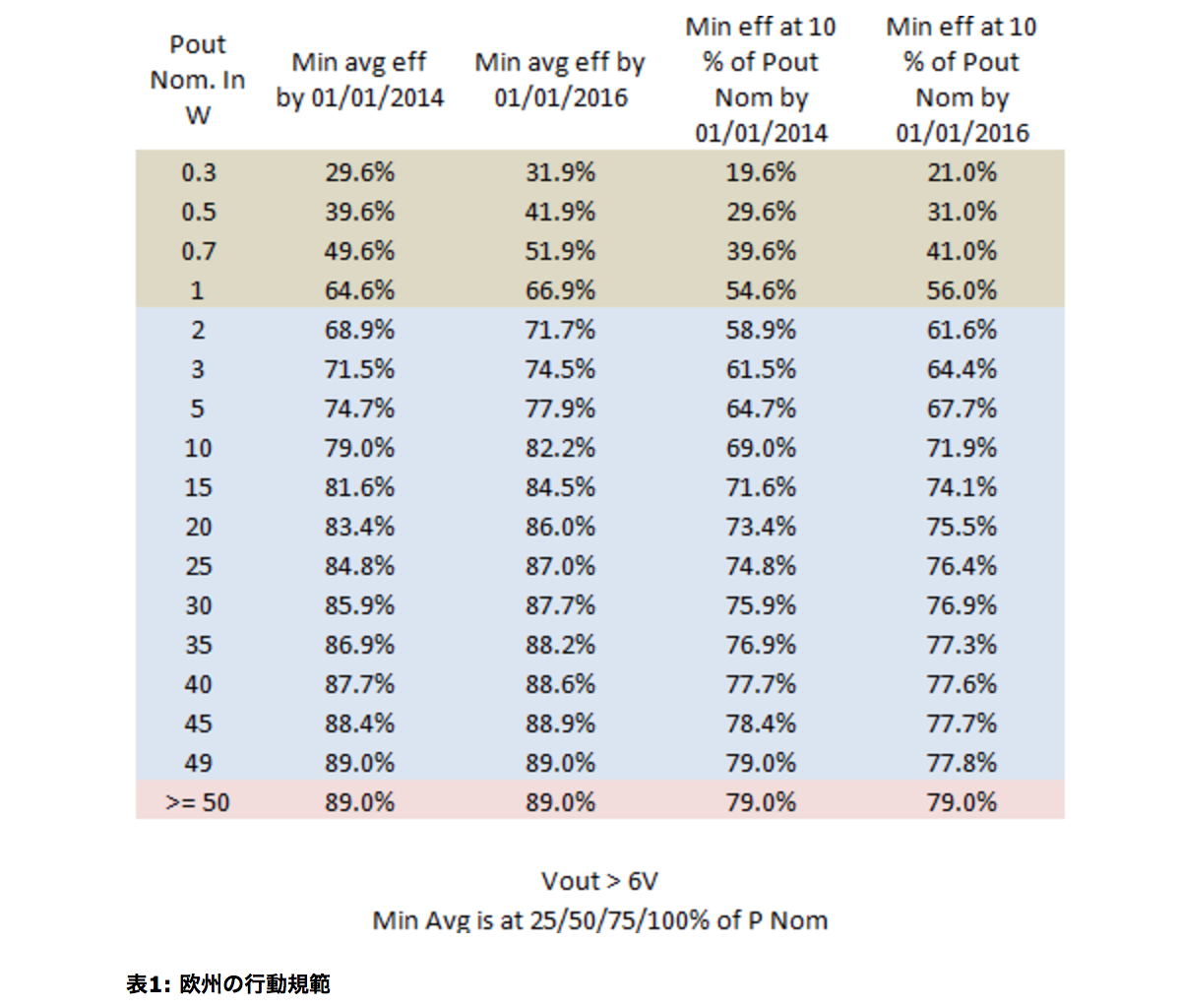

米国および欧州のエネルギー省は、2014年版および2016年版の新しい効率基準を定義しました。

欧州の行動規範に目を向けると、2014年から2016年の間に40W電源の最小平均効率を約1%改善しなければなりません。

効率の推移については、表1を参照してください。

これらの勧告に加えて、当社のお客様の中には、製造するアダプタに米国および欧州規格よりも高い目標値を課している企業もあります。

実際、全体の効率が向上すると電力損失が低くなるので、アダプタのサイズとコストを低減できます(例えば、ヒートシンクの小型化)。

さらに小型化を図るために、スイッチング周波数を高くすることができます。

この技術のおかげで、磁気回路の容積を低減できます。

例えば、50kHzまたは60kHzのスイッチング周波数で動作させてRM8磁気コアを使用する代わりに、300kHzの周波数で動作させればRM6タイプ(1825mm3~837mm3)のような、さらに小型のコアを使用できるようになります。

この設計を動機付ける2つの主なターゲットは効率とサイズです。

上述したとおり、この2つは関連しています。

小型化するには、損失を抑えて効率を高くする必要があります。

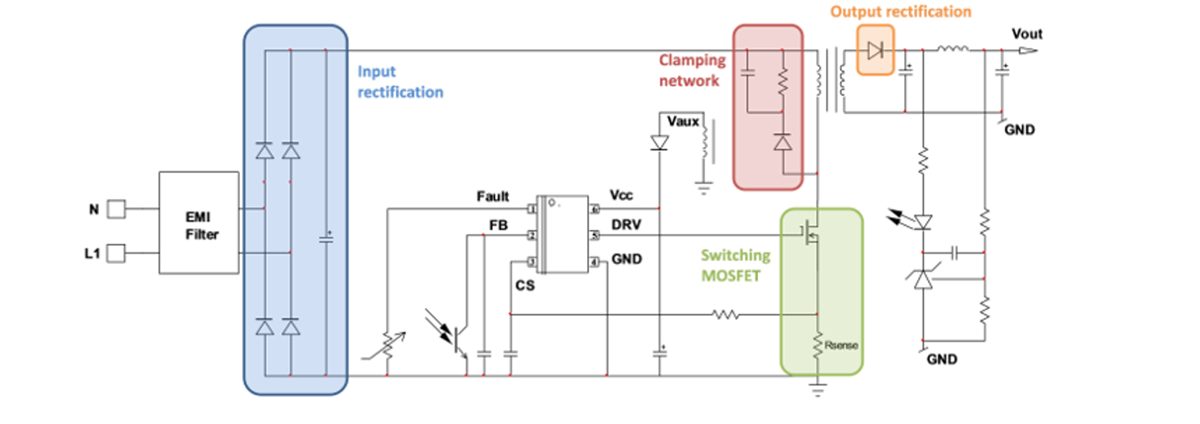

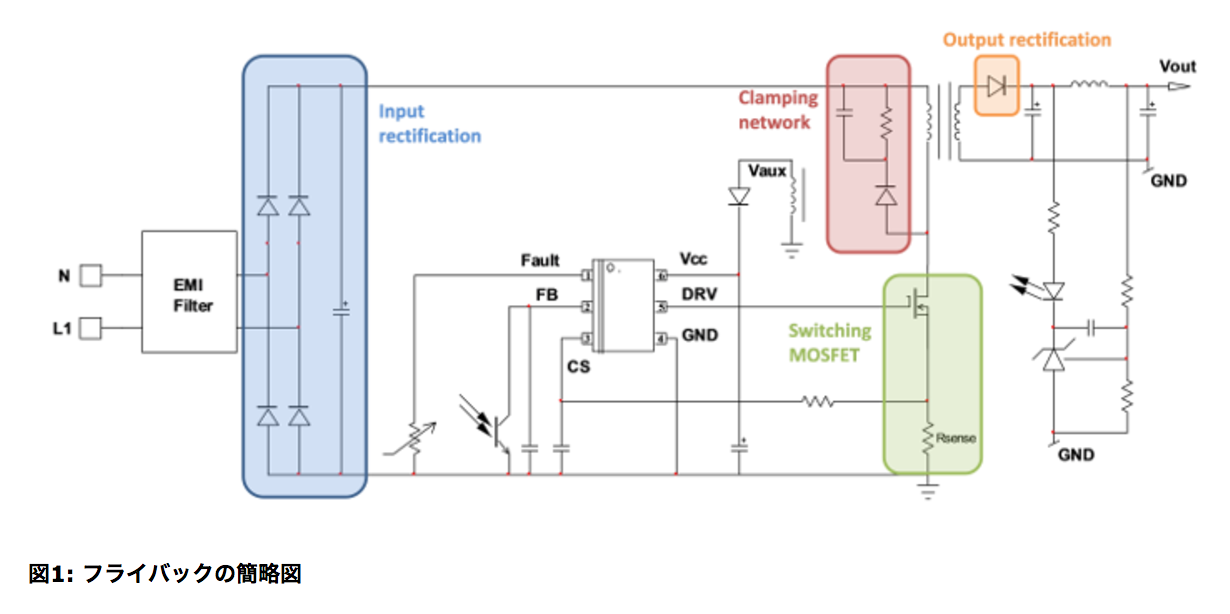

フライバック電源では、以下の箇所で大部分の損失が生じます。

- フロントエンド:ダイオード・ブリッジおよびバルク・コンデンサ

- トランス:鉄損および銅損

- 一次側スイッチングMOSFETおよびセンス抵抗:ドレイン-ソース間rDS(on) およびスイッチング損失

- MOSFETクランプ・ネットワーク: RCDクランプまたはTVS(過渡電圧サプレッサ)

- 二次側整流:出力ダイオードまたは同期整流

- 出力コンデンサ: ESR(等価直列抵抗)

- Vcc減失

各主要要素は、入力電圧に関係なく、全負荷時に90%以上の効率になるよう注意深く選択されています。

例えば入力整流の場合:ダイオードについてはより低い順方向電圧と動的抵抗が選択されており、バルク・コンデンサについては低いESRが選択されています。

一次側スイッチングMOSFETの周辺でも、同じ検討がなされてきました。

ドレイン-ソース間オン抵抗(rDS(ON))に関連する導通損失とスイッチング損失の間でトレードオフを見つける必要があります。

大部分が全ゲート電荷量に関連します。

この設計ではスイッチング周波数が高くなっているため、スイッチング損失がさらに重要です。

オン・セミコンダクターはこの高スイッチング周波数戦略に従って、デモ・ボードを設計しました。

このボードに使用されるコントローラは、NCP1339疑似共振(QR)コントローラであり、高電圧(HV)起動電流源とX2コンデンサ放電機能を特徴としています。

コンバータは、二次側にも同期整流コントローラ(NCP4305)を使用して、58.7×38.2cmのボード上にレイアウトされています。

以下の写真は組立て済みの試作品を示しています。

入手可能な部品を使用して電力密度を高めるために、レイアウト・フェーズでは慎重な設計が行われ、電力密度は0.80W/cm3に達しました。

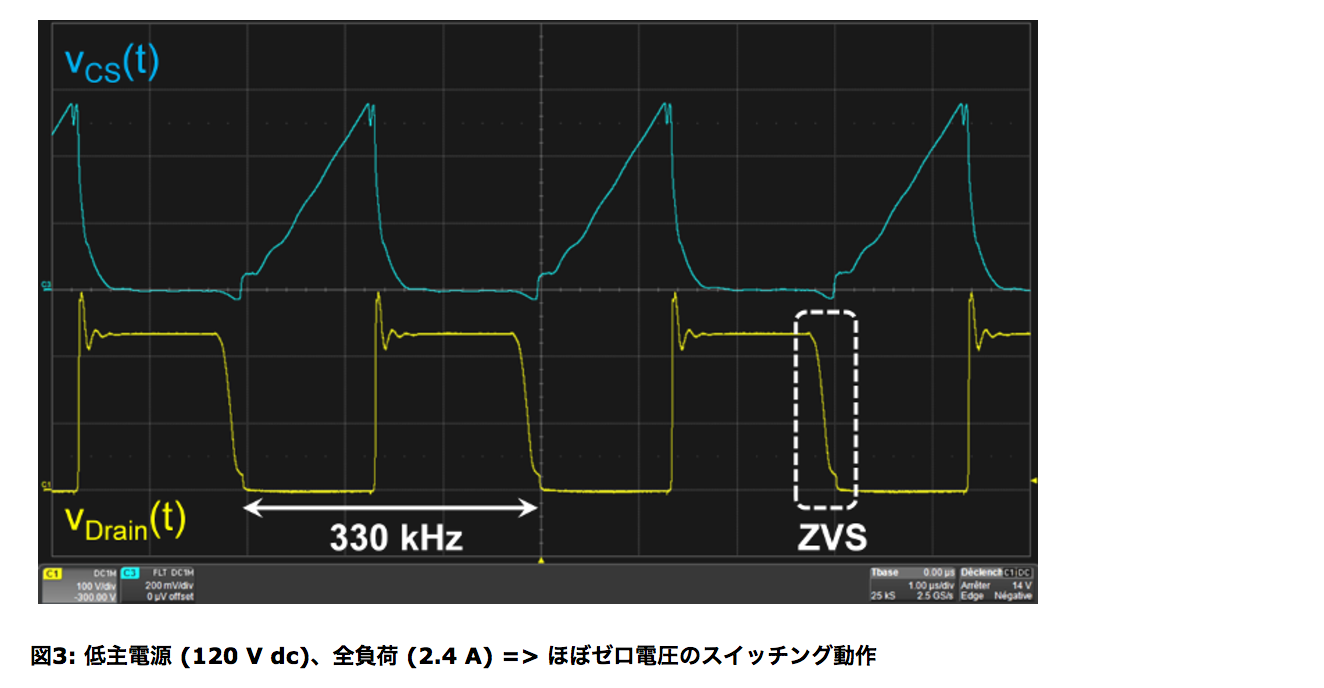

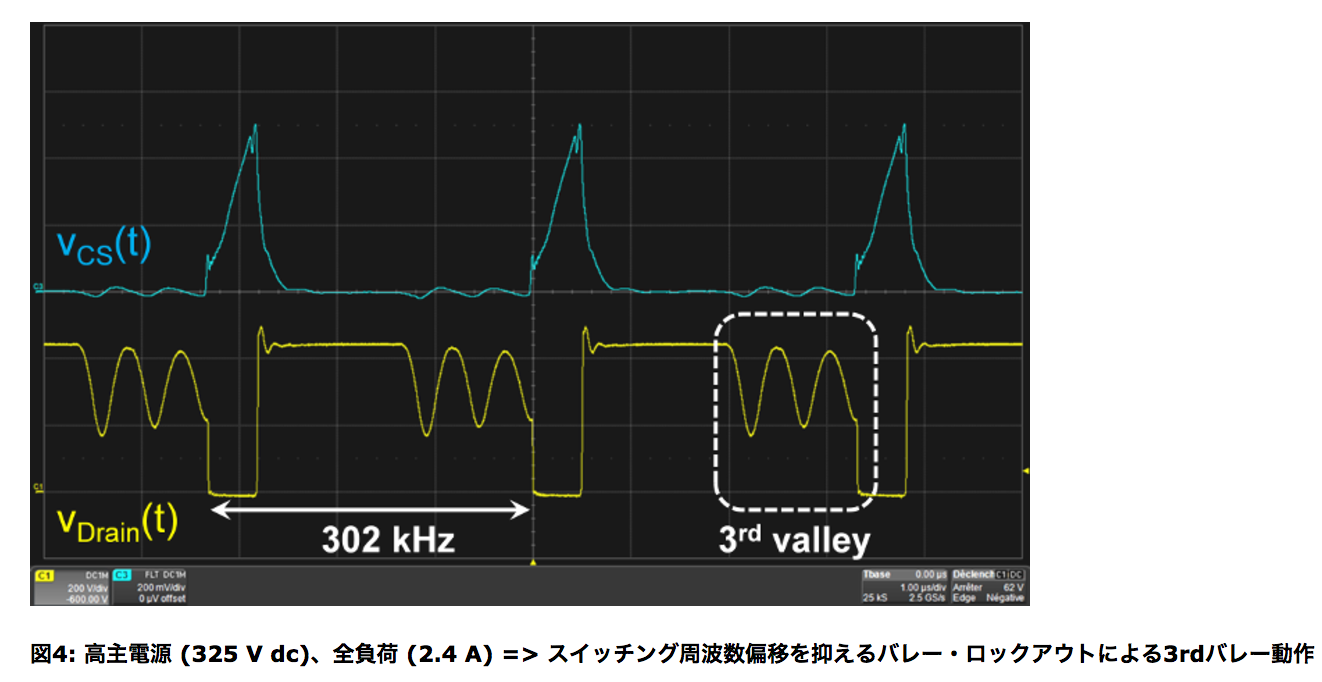

代表的な波形を以下に示します。

一部の波形は異なる条件で撮影されています。

QR動作に関連する従来からの問題は、いわゆるバレー・ホッピング現象です。

コントローラはドレイン(最小電圧)上のバレーの発生に同期するので、入力条件および出力条件の変化時のバレーの変化は、離散的周波数のステップを生じます。

このステージではピークが固定されるため動作が不安定になり、音響ノイズが誘起される可能性があります。

この問題は、独自のロックアウト回路を内蔵するNCP1339によって解決されます。

このコントローラはバレーが選択されるとロックインし、フィードバック電圧が大幅に上昇または低下するまでロックイン状態のままです。

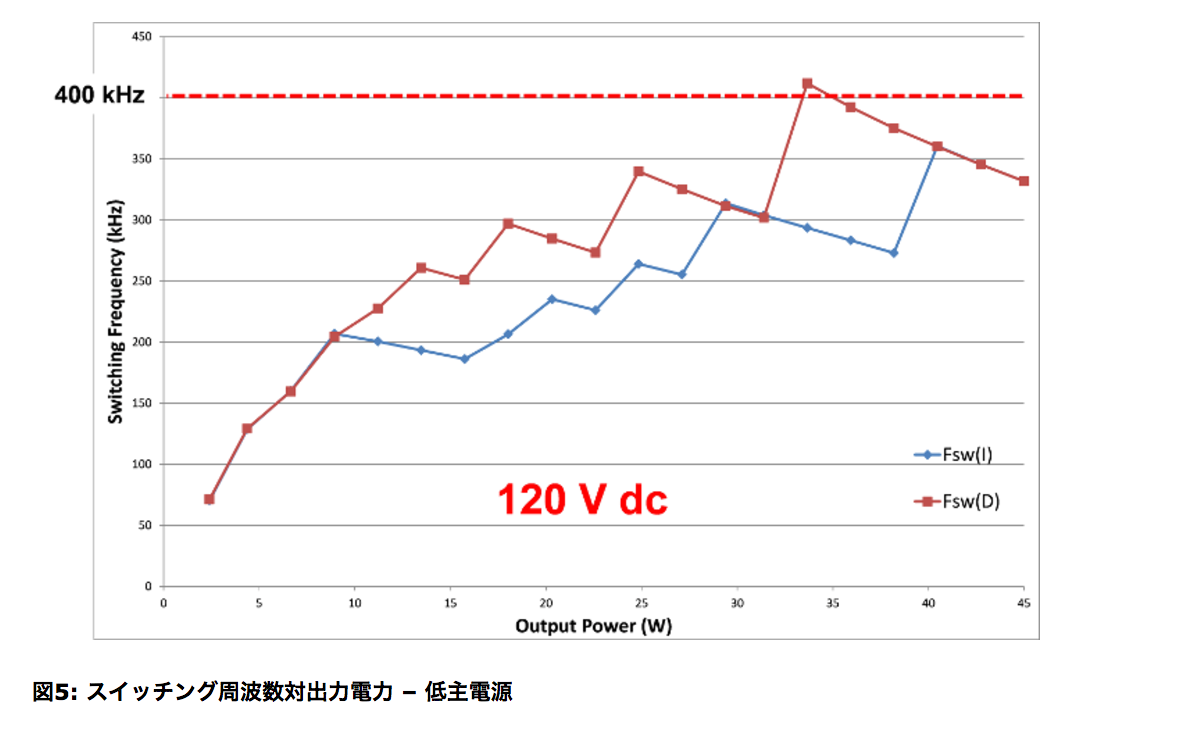

このロックアウト機能と電圧制御発振器を組み合わせたことにより、軽負荷状態では、出力電力に関係なくスイッチング周波数偏移が残ります。

低主電源および高主電源で周波数偏移がキャプチャされました。

この図から分かるように、スイッチング周波数は従来式のフライバック設計に比べて高くなっています(固定周波数60〜70kHzコンバータに対して350kHz)。

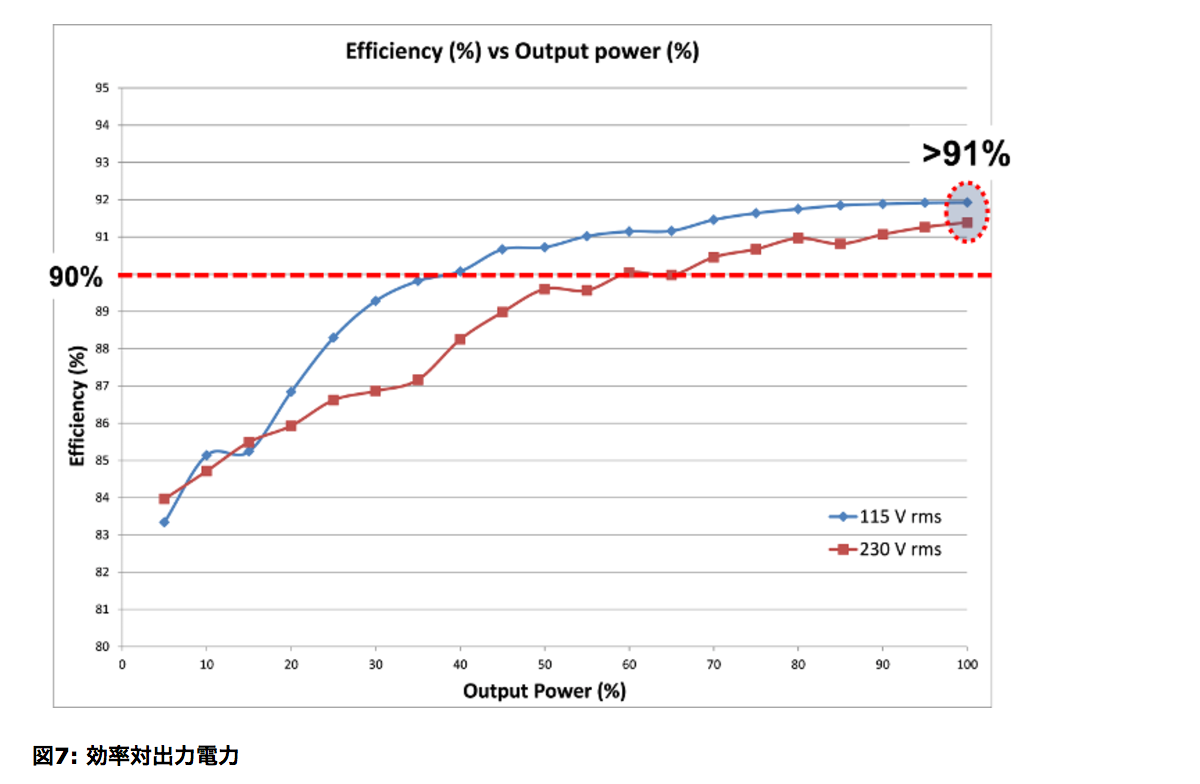

このデモ・ボードの周辺でもう一つの重要な測定(すなわち、効率の測定)が実施されました。

表1に示すとおり、欧州規格および米国規格は2016年により厳格な内容に変更される予定です。

45Wアプリケーションの場合、平均効率は最大負荷の10%において、88.9%および77.7%以上に向上するでしょう。

表2および図7に示すように、弊社が設計したボードはこれらの要件に適合しています。

最後のチェックポイントは無負荷時のスタンバイ消費電力です。

この種のアダプタの代表的な用途はラップトップ製品向けです。

ほとんどの場合、デバイスがフルに充電されるかあるいは電源がオフになっているときでも、機器の電源は主電源に差し込まれたままです。

このような状態では、充電器の消費電力をできるだけ低く抑えなければなりません。

高電圧起動電流源と埋め込みX2コンデンサ放電回路のおかげで、通常なら高電圧電源に恒久的に接続される抵抗ストリングが省略され、スタンバイ入力の消費電力は115Vrmsで30mW以下(正確には25mW)、230Vrmsで31mW以下になります。

このデモ・ボードに関連するすべての技術情報は、次のオン・セミコンダクターのウェブサイトで入手できます。

http://www.onsemi.jp/PowerSolutions/evalBoard.do?id=NCP1339GGEVB

出典:『高密度QRフライバック・コンバータ技術で電源実装の進歩を実現』オン・セミコンダクター